POWER-SUPPLY CIRCUITS

## An Accurate Control Loop Model for Current-Mode Step-Down Controllers

Peak current-mode control is preferred by power supply designers because it provides a first-order frequency response characteristic in the control-to-output transfer function. A control-loop design procedure based on the first-order model predicts a phase margin close to 90 degrees. It is found, however, that the phase margin obtained in practice is far less than 90 degrees depending on choice of crossover frequency, operating duty cycle, and amount of slope compensation used. This is due to the sampling effect of the control-loop current comparator. The following application note describes a control-loop design procedure for the MAX1954A current-mode controller that considers this sampling effect and accurately predicts phase margin. This analysis is not specific to the MAX1954A, however, and applies to most current-mode step-down ICs sold today.

## **The First-Order Model**

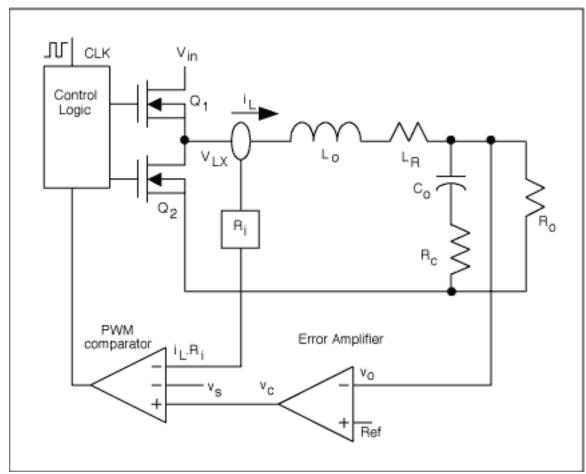

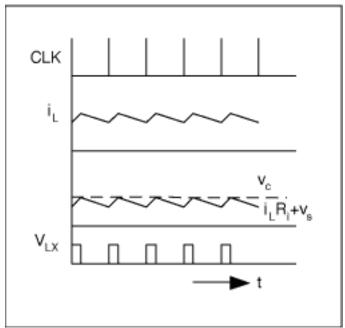

A typical current-mode control loop for a step-down DC-DC converter is shown in Figure 1. A constant frequency clock, CLK, turns on the high-side MOSFET. Q1 turns off when the scaled-output inductor current at the inverting input of the PWM comparator exceeds the control voltage,  $v_c$ . Thus vc programs the peak inductor current to maintain the output voltage,  $v_o$ , constant. This results in a current source behavior for the output inductor, and therefore a first-order control-to-output transfer function. A compensating ramp,  $v_s$ , is applied to a second inverting input of the PWM comparator to prevent subharmonic instability at duty cycles greater than 0.5 and to improve noise immunity. The relevant waveforms for current-mode control are shown in Figure 2.

Figure 1. Peak Current-Mode Control Scheme

Figure 2. Current-Mode Control Waveforms

The control-to-output transfer function generally used for peak current-mode controller design is given in the following equation:

$$G_c(s) = \frac{R_0}{R_i} \cdot \frac{(1 + s/\omega_z)}{(1 + s/\omega_p)}$$

The above equation predicts a pole,  $\omega_p$ , due to the output capacitance,  $C_o$ , and load resistance,  $R_o$ . The equation also predicts a zero,  $\omega_z$ , due to the output capacitance and its equivalent series resistance (ESR),  $R_c$ . The gain and phase predicted by the above model differ from that observed in practice because of the "sample and hold" effect in the PWM comparator that results from the current waveform getting sampled only once every cycle. It has been shown in [1] that the simple peak current-mode control model in the above equation must be modified to include a double pole at one half the switching frequency to account for the sampling effect.

## **Procedure for Predicting the Phase-Margin**

Following is a description of a control-loop design procedure for the MAX1954A current-mode controller that considers this high-frequency effect and predicts the phase margin accurately. The MAX1954A evaluation kit circuit diagram is used to carry out the design. Both the MAX1954A evaluation kit data sheet and the MAX1954A data sheet are available.

The accurate control-to-output transfer function is given by the following equation:

$$G_{c}(s) = \frac{R_{o}}{R_{i} \cdot \left[1 + \frac{R_{o} \cdot T_{s}}{L_{o}} \cdot (m_{c} \cdot (1 - D) - 0.5)\right]} \cdot \frac{(1 + s/\omega_{z})}{(1 + s/\omega_{p1})} \cdot \frac{1}{\left(1 + \frac{s}{\pi Q_{c}} + \frac{s^{2}}{T_{s}}\right)^{2}}\right]$$

where duty cycle  $D = \frac{V_O}{V_{im}}$ , sampling effect quality factor  $Q_C = \frac{1}{[\pi.(m_C.(1-D)-0.5)]}$ , slope  $m_C = 1 + \frac{S_C.L_O}{(V_{im}-V_O)R_i}$ ,  $\omega_{Pl} = \frac{1}{R_C.C_O} + \frac{T_S}{L_O.C_O}$ .  $(m_C.(1-D)-0.5)$ ,  $\omega_z = \frac{1}{R_C.C_O}$ ,  $T_S$  compensation factor is the switching period, is the slope of the compensating ramp, if any, is the product of the current-sense amplifier gain and current-sense resistance (high-side MOSFET  $R_{ds\_on}$  for the MAX1954A),  $R_O$  is the load resistance,  $V_O$  is the output voltage, and  $V_{in}$  is the input voltage. For the MAX1954A evaluation kit circuit, the following design parameters apply:

$$V_{in} = 11V$$

$V_{o} = 1.5V$

$D = 0.136$

$m_{c} = 1$

$S_e = 0$  (slope compensation applied at this duty cycle in the MAX1954A is negligible)

$T_s = 3.3 \mu S$

$R_c = 9m\Omega$

$C_0 = 180 \mu F$

$L_0 = 2.18 \mu H$

$R_0 = 0.3125\Omega$

$R_i = 0.063$

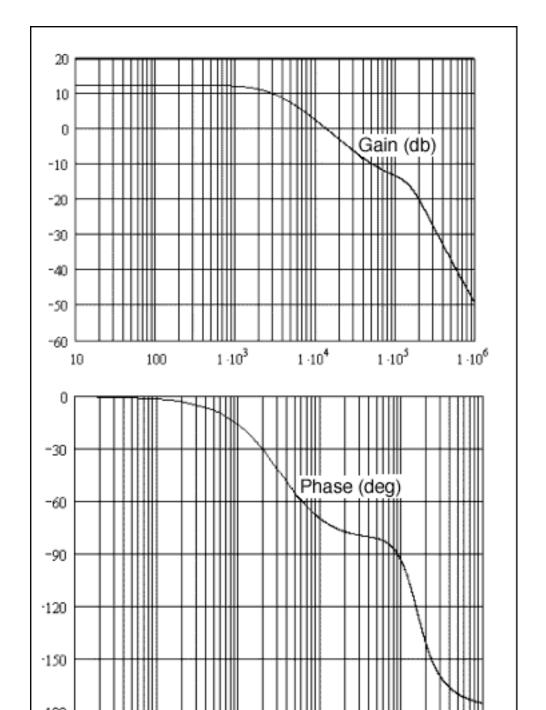

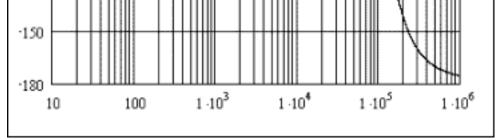

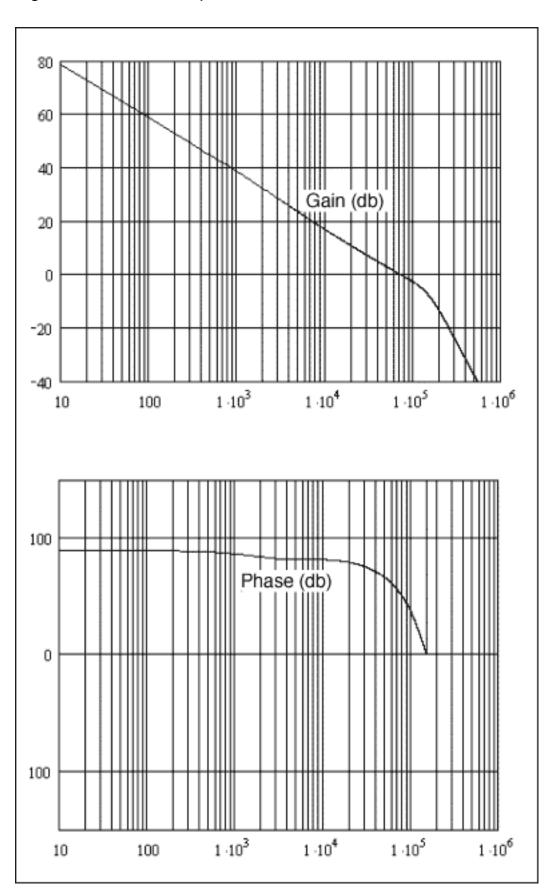

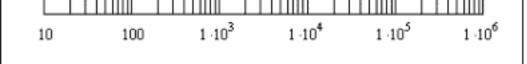

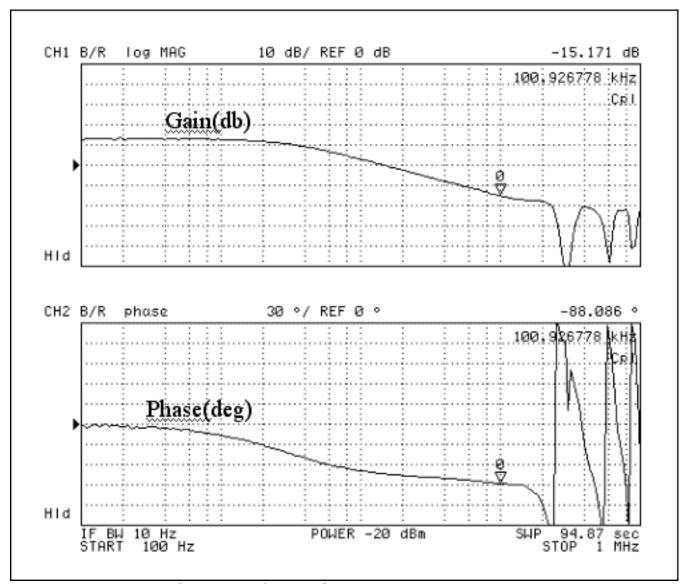

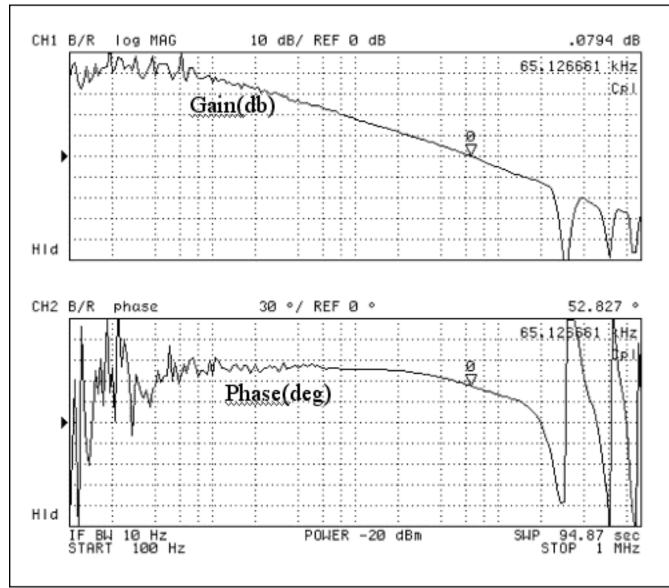

The compensation network is designed as recommended in the MAX1954A data sheet. The control-to-output transfer function and the open-loop gain predicted by the accurate model are plotted using MathCad and are shown in Figure 3 and Figure 4 respectively. The actual control-to-output loop gain and open-loop gain transfer functions measured on the MAX1954A evaluation kit are shown in Figure 5 and Figure 6 respectively.

Figure 3.Control-to-Output Gain and Phase Plots from MathCad

Figure 4. Open-Loop Gain and Phase Plots from MathCad

Figure 5. Measured Control-to-Output Gain and Phase Plots

Figure 6.Measured Open-Loop Gain and Phase Plots

The control-to-output gain and phase predicted by the model match the measured values closely. At 101kHz, the model predicts -13.5db gain and a phase lag of -95 degrees. The measured plots show -15.1db gain and -88 degrees phase lag. The open-loop gain and phase plot from the model shows a crossover frequency of about 70kHz and a phase margin of 56 degrees. The measured plots show a crossover frequency of 65kHz and phase margin of 52.8 degrees. The first-order model would have predicted a phase margin of about 90 degrees, and may have implied that wider component tolerance was acceptable. To obtain the correct stability margins, therefore, a model that considers sampling effect is recommended even for peak current-mode designs with low crossover.

[1] A New Small Signal Model for Current Mode Control, Raymond B. Ridley, PhD dissertation, Virginia Polytechnic Institute and State University, 1990.

## **More Information**

MAX1954A: QuickView -- Full (PDF) Data Sheet -- Free Samples